ADコンバータ(ADC)は、最新のデータ収録システム(別名DAQまたはDASシステム)の基本的なブロック構築の1つです。データ収録システム内のADコンバータの主な目的は、シグナルコンディショナで調整されたアナログ入力信号をデジタルデータに変換し、データ収録システムが処理,表示,保存,解析できるようにすることです。

関連ページ

ADコンバータ(ADC)の主な種類

現在使用されているADCには、主に5つの種類があります。

- 逐次比較ADC(SAR)

- デルタシグマADC(ΔΣ)

- デュアルスロープADC

- フラッシュADC

- パイプラインADC

ADCの主な機能と特長

ADCには次のものが含まれます。

- サンプルレート - ADCはアナログをデジタルにどれだけ速く変換できるか?

- ビット分解能 - ADCはアナログをデジタルにどれだけの精度で変換できるか?

これらの基本的な仕様をそれぞれ詳しく見てみましょう。

サンプルレートとは何ですか?

信号がアナログドメインからデジタルデータに変換される速度は、サンプルレートまたはサンプリング周波数と呼ばれます。それはアプリケーションに依存する値です。たとえば、気圧は数分または数時間にわたって非常にゆっくりと変化するため、実際には毎秒1回以上サンプリングする必要はありません。

一方、レーダー信号を計測する場合は、毎秒数億回、場合によっては毎秒数十億回のサンプリングを行う必要があります。

ADCサンプリングレート

データ収録の世界では、AC電圧と電流,衝撃と振動,温度,ひずみ,圧力などを計測します。これらの信号とセンサは、一般的にDCから毎秒200,000サンプル(200 kS / s)のサンプルレートを必要としますが、一部のアプリケーションでは最大1,000,000サンプル/秒(1 MS / s)のサンプリングが必要です。

サンプルレートは通常、計測のT(時間)またはX軸と呼ばれます。

サンプルレートが重要なのはなぜですか?

信号とその可能な最高周波数を理解することは、正確な計測を行うために非常に重要です。たとえば、加速度センサの出力を計測するとします。

最大周波数が100 Hzの振動が発生すると予想される場合は、サンプルレートを少なくとも2倍(ナイキスト周波数)に設定する必要があります。 しかし実際には、信号形状を高品質で表現するには、10倍のオーバーサンプリングの方が適しています。 したがってこの例では、サンプルレートを1000 Hzに設定して計測を行います。

理論的には問題ないはずですが、信号周波数が実際にはそれほど高くならないことをどのようにして確認しますか? サンプリングが間違っていた場合、システムは入力信号を正確に計測できません。 そして、実際にはサンプリングを極端に設定すると計測値が完全に間違っている可能性さえあります。

エイリアシングを理解するには、自動車のホイールが回転する様子をカメラが毎秒24フレームで撮影している古い映画が参考になります。さまざまな速度で、ホイールが逆回転しているか、まったく動いていないように見えます。また、カメラのシャッタースピードがヘリコプターのブレードと同期していて、ヘリコプターが空中にぶら下がっており、ブレードがまったく動いていないように見えるビデオを見たことがあるかもしれません。

これは、ホイールの回転周波数とカメラの撮影速度の調和関係によって引き起こされる一種のストロボ視覚効果です

ADCで電圧信号をデジタル化するという点では、サンプルレートを適切に設定することが重要です。設定が高すぎると、処理能力を浪費し、データファイルが不必要に大きくなり、解析が難しくなります。

一方、設定が低すぎると次の2つの問題が発生する可能性があります。

- 重要な動的信号成分を計測できていない

- エイリアス信号(システムにアンチエイリアスフィルタリングがない場合)によって間違った信号で計測してしまう

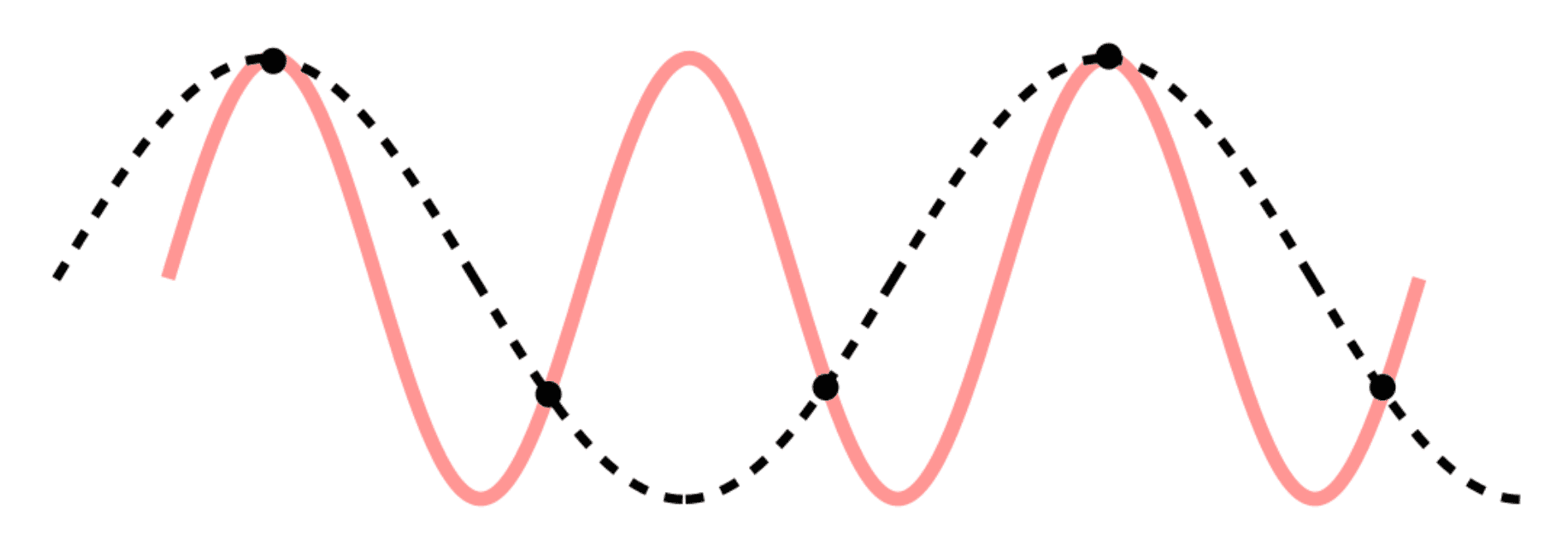

元の信号と比較してサンプリングが低すぎるために発生した、偽の信号(エイリアス)の黒の表示

元の信号と比較してサンプリングが低すぎるために発生した、偽の信号(エイリアス)の黒の表示

※画像はパブリックドメイン

最適なサンプルレート

計測者はこの時点で、信号周波数よりもはるかに速くサンプリングすることを考えるかもしれません。そしてそれはアンダーサンプリングの問題を解決するかもしれません。しかしこれにより新しい問題が発生します。収録されるデータの量を大幅に増やすと、データの処理,保存,解析に問題が発生します。また、システムによっては高速サンプリングができない場合があります。

幸いほとんどが冗長な大量のデータで負荷をかけずにエイリアシングを回避する、より良い方法があります。それはアンチエイリアシングフィルタリングです。

アンチエイリアシングフィルタリング(AAF)

ADCの前にアナログドメインでフィルタ処理すると、エイリアシング問題が発生するのを防ぐことができます。目的の周波数範囲を収録するために十分高いサンプルレートを設定することは重要ですが、少なくともアンチエイリアシングフィルタ(AAF)を使用すると、誤った信号が収録データを破壊することを回避できます。

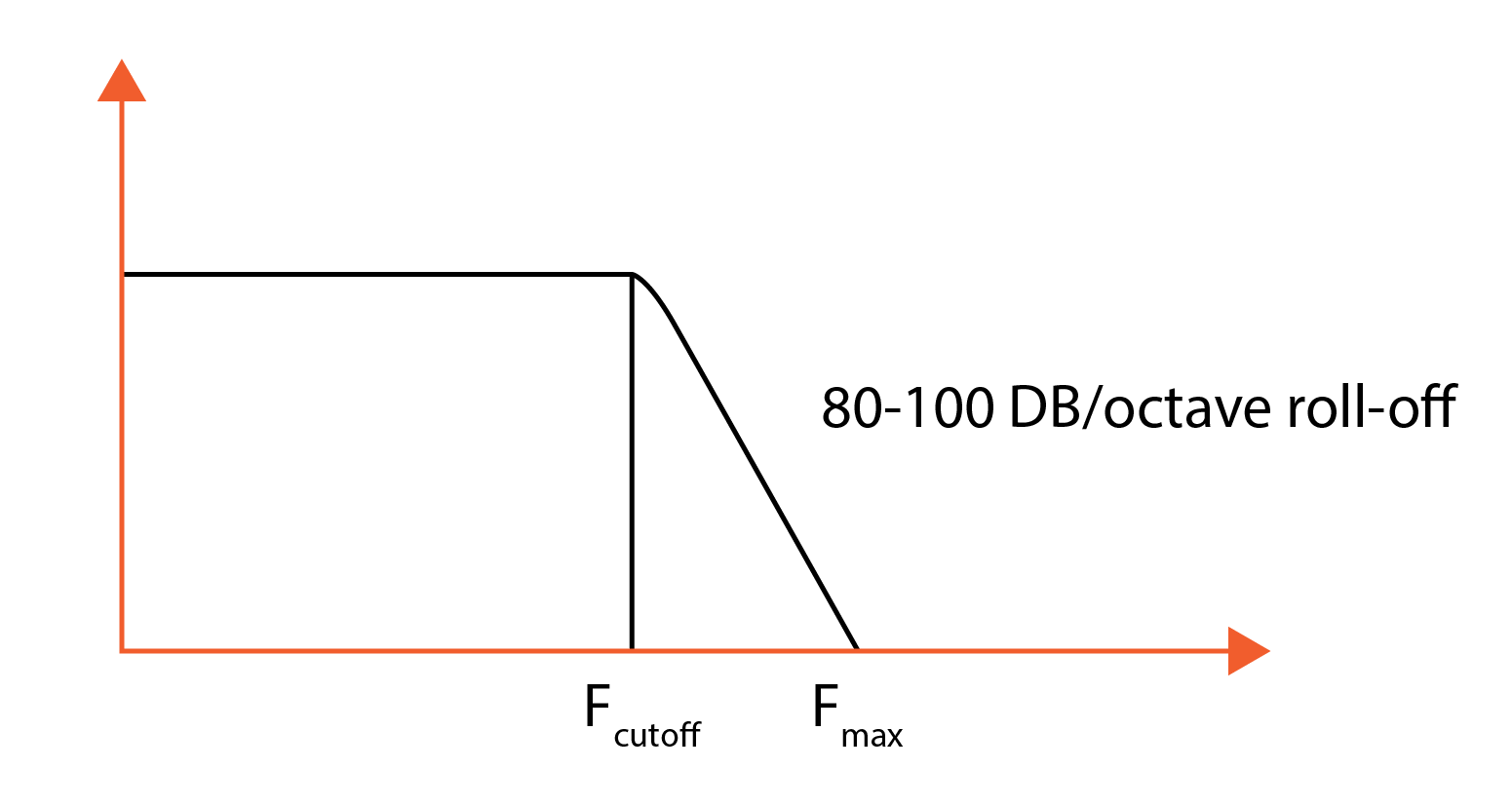

理想的なAAFは、ナイキスト周波数(本質的にサンプルレートの半分)で非常にフラットな通過帯域と非常に鋭いカットオフを備えています。

アンチエイリアシングフィルタのロールオフ図

アンチエイリアシングフィルタのロールオフ図

一般的なAAF構成:ADCの前の急峻なローパスアナログフィルタは、ADCの最大帯域幅の半分を超える信号が通過するのを防ぎます。

これは、SIRIUS-HS モジュールに搭載されている16ビット SAR ADCが行っていることです。

ただし、24ビットデルタシグマADCを備えたDAQシステム(DEWESoftシステム等)には、ADC自体に追加のDSPフィルタがあり、ユーザが選択したサンプルレートに基づいて自動的に設定されます。

ビット分解能とは何ですか、なぜ重要なのですか?

前のセクションで説明したサンプルレートにはデジタルデータストリームの時間(TまたはX)軸が含まれますが、ビット分解能またはビット数には振幅(Y)軸が含まれます。

データ収録機器の初期には8ビットADCが一般的でした。現在のDAQシステムの世界では、24ビットADCは動的計測用に設計された殆どのデータ集録収録システムの標準であり、16ビットADCは一般にDAQシステムの最小分解能と見なされています。さらに12ビットADCを利用するいくつかのローエンドシステムがあります。

解像度の各ビットは実質的に可能な解像度を2倍にするため、24ビットADCを備えたシステムは 2^24 = 16,777,216の分解能を提供します。したがって、1ボルトの入力信号は、Y軸上で 1,600 万以上のステップに分割できます。

24ビットADCの16,777,216ステップは、16ビットADCの理論上の最大65,656ステップよりも大幅に優れています。したがって、波形の形状はそれに応じてより正確になり、精度が高くなり、分解能が高くなります。これは時間軸にも当てはまります。

24ビットの分解能(オレンジ)と16ビットの分解能(グレー)

DualCoreADC®テクノロジとその重要性

振幅軸に関して、計測者が長年直面している1つの課題はダイナミックレンジです。たとえば、信号が通常5ボルト未満であっても、場合によっては劇的に大きくなる場合はどうなるでしょうか。ADCの分解能を0-5Vのデータに対応するように設定した場合、信号がそれを超えて上昇するとシステムは完全にオーバーレンジになります。

1つの解決策は、異なるゲインに設定された2つのチャネルを使用します。0-5Vデータに対して1チャネルを参照し、より高い振幅データに対してもう1チャネルを参照することです。しかし、これはとても非効率的です。すべての入力信号に2つのチャネルを使用することはできません。同じ作業を行うには、2倍のDAQシステムが必要になります。さらに、各テスト後のデータ解析が非常に複雑になり、時間がかかります。

DEWESoftのDual Core ADC®テクノロジは、チャネルごとに2つの個別の24ビットADC(1チャネルに2つのADCを搭載)を使用し、信号レベルに応じてリアルタイムに自動でADCを切り替え、シームレスなチャネルを作成することでこの問題を解決します。これらの2つのADCは、常に入力信号の高ゲインと低ゲインを計測します。これにより、センサの可能な全計測範囲が得られ、信号がクリップされるのを防ぎます。

【動画】DualCoreADC®

テクノロジにより、SIRIUSは130 dBを超えるS / N比と160 dBを超えるダイナミック

レンジを実現します。これは一般的な24ビットシステムよりも20倍優れており、ノイズは20倍少なくなります。

関連ページ

チャネルごとのマルチプレクスADC vs シングルADC

データロガーや産業用制御システムなどのローエンドDAQシステムでは、マルチプレクスA / Dカードが使用されることがよくあります。これは、入力チャネルごとに個別のADCチップを備えたA / Dカードよりも安価であるためです。

マルチプレクスADCシステムでは、1つのADCを使用して複数の信号をアナログからデジタル領域に変換します。これは、複数チャネルのアナログ信号を一度に1つずつADCにマルチプレクスすることによって行われます。

これは低コストですが、一度に変換できる信号は1つだけなので、信号を時間軸上で正確に整列させることはできません。したがって、チャネル間には常に時間のずれがあります。短時間のスキューエラーが特定のアプリケーションに無関係である場合、これは問題になりません。同じことがシステム内で使用されるアナログデバイスにも当てはまります。形状,フィット,機能の点でアプリケーションに最適なものを選択することが重要な要素です。

さらに、最大サンプルレートは常にサンプリングされるチャネルの数で除算されるため、1つまたは少数のチャネルのみがサンプリングされる場合を除いて、チャネルあたりの最高サンプルレートは通常、マルチプレクスシステムでは低くなります。

現在のデータ収録システムでは、マルチプレクスADCシステムは、精度や速度よりもコストが重要なローエンドシステムで主に採用されています。

5つの主要なADCテクノロジ

現在使用されているADCには5つの主要なタイプがあります。各タイプにはビット分解能とサンプルレートの特性に基づいて、それぞれの用途があります。各タイプを見てそれらがどのように機能するか、そして現在どのように使用されているかを見てみましょう。

主要なADCタイプの比較

| ADCタイプ | 長所 | 短所 | 最大分解能 | 最大サンプル レート |

主な用途 |

|---|---|---|---|---|---|

| 逐次比較(SAR) | 優れた速度/分解能比 | 固有のアンチエイリアス保護は無し | 18ビット | 10 MHz | データ収録 |

| デルタシグマ(ΔΣ) | 高いダイナミック性能、固有のアンチエイリアス保護 | 不自然な信号のヒステリシス | 32ビット | 1MHz | データ収録、ノイズと振動、オーディオ |

| デュアルスロープ | 正確で安価 | 低速 | 20ビット | 100 Hz | 電圧計 |

| パイプライン | とても早い | 限られた分解能 | 16ビット | 1 GHz | オシロスコープ |

| フラッシュ | 最速 | 低ビット分解能 | 12ビット | 10 GHz | オシロスコープ |

各タイプに独自の利点と欠点があるため、特定のアプリケーションに適しています。

タイプ別に特長を見てみましょう

逐次比較ADC(SAR)

DAQの世界で重要な要素であるADCは、SARアナログデジタルコンバータ(逐次比較レジスタ)です。速度と分解能の優れたバランスを提供し、優れた忠実度でさまざまな信号を処理します。

それは古くから使用されているため、SAR設計は安定していて信頼性が高く、チップは比較的安価です。1つのADCチップで複数のチャネルを入力する方式(マルチプレクスA/Dボード)、または各入力チャネルにADCを搭載し同期サンプリングを実現する両方に使用されます。

一般的なSARブロック図

ほとんどのADCのアナログ入力は5Vです。そのため、ほぼすべてのシグナルコンディショナが最大5Vに調整された出力をADCに供給します。一般的なSAR ADCは、シグナルコンディショナから供給されたアナログ電圧を取り込むサンプルホールド回路を使用します。

内蔵DACは、サンプルのデジタルコード出力に等しいアナログ基準電圧を生成し、回路を保持します。これらは両方ともコンパレータに送られ、比較結果がSARに送信されます。このプロセスは、実際の信号に最も近い値が見つかるまで、ADC自体のビット分解能である「n」回連続して実行されます。

SAR ADCには固有のアンチエイリアシングフィルタリング(AAF)が無いため、これがDAQシステムによってADCの前に追加されない限り、計測者が低すぎるサンプルレートを選択すると、誤った信号(エイリアス)がSAR ADCによってデジタル化されます。エイリアスは、デジタル化後に修正することができないため大きな問題になります。

エイリアスソフトウェアで修正する方法はありません。すべての入力信号のナイキスト周波数よりも常に高速でサンプリングするか、ADCの前と内部で信号をフィルタリングすることにより、これを防ぐ必要があります。

長所

- 必要なコンパレータが1つだけのシンプルな回路

- デルタシグマADCと比較して高いサンプルレートが可能

- 自然な波形と不自然な波形をうまく処理

短所

- アンチエイリアシングフィルタを外部で追加する必要がある

- デルタシグマADCと比較してビット分解能とダイナミックレンジが制限される

用途

SAR ADCのアプリケーションには、ローエンドのマルチプレクスADCシステムからチャネルごとの高速シングルADCシステムまでのDAQシステム、産業用制御および計測、CMOSイメージングが含まれます。

デルタシグマADC(ΔΣ)

新しいADCは、デルタシグマADCです。これは、DSPテクノロジを利用して振幅軸の分解能を向上させ、SAR設計に固有の高周波量子化ノイズを低減します。

デルタシグマADCの複雑で強力な構造は、可能な限り多くの振幅軸分解能を必要とするダイナミックアプリケーションに最適です。デルタシグマADCがオーディオ,サウンド,バイブレーション,および幅広いハイエンドデータ収録アプリケーションで一般的に使用される理由です。また、高精度の産業用計測アプリケーションでも広く使用されています。

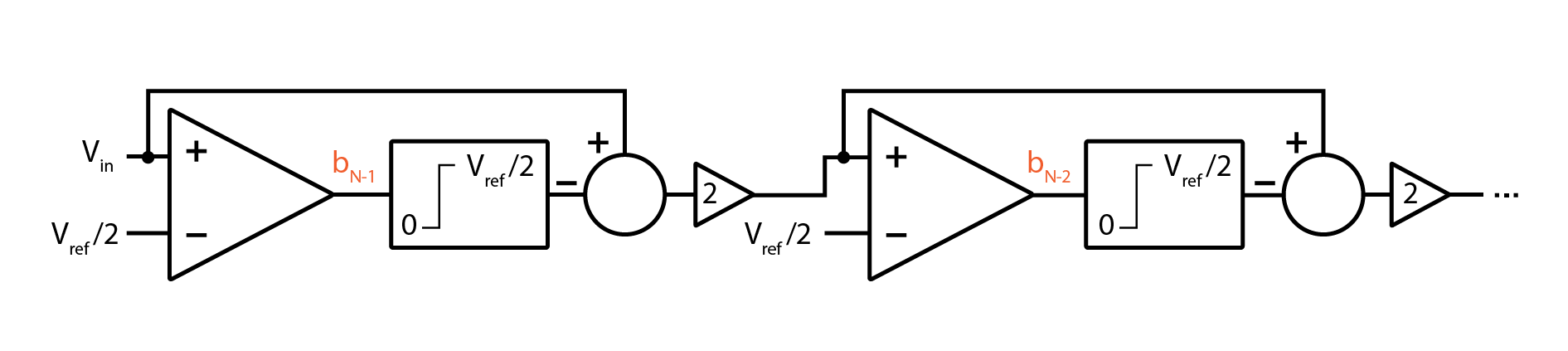

一般的なデルタシグマADCブロック図

DSPに実装されたローパスフィルタは、実質的に量子化ノイズを排除し、優れた信号対ノイズ性能をもたらします。

デルタシグマADCは、選択したサンプルレートよりはるかに高い信号をオーバーサンプリングすることで機能します。DSPは、ユーザが選択したレートでこのオーバーサンプリングされたデータから高分解能のデータストリームを作成します。このオーバーサンプリングは、選択したサンプルレートより数百倍も高くなる場合があります。この方法は非常に高分解能のデータストリーム(24ビットが一般的)を作成し、多段(複数のカットオフ周波数)のアンチエイリアシングフィルタリング(AAF)を可能にするという利点があり、誤った信号をデジタル化することが事実上不可能になります。ただし、これは一種の速度制限を課すためデルタシグマADCは通常SAR ADCほど高速ではありません。

長所

- 高分解能出力(24ビット)

- オーバーサンプリングにより量子化ノイズが低減

- アンチエイリアスフィルタリング

短所

- 約200kS/sのサンプルレートに制限

- SARと同様に不自然な形状の波形は扱わない

用途

デルタシグマADCのアプリケーションとして、高精度データ収録,特にノイズと振動,産業用バランシング,ねじりと回転振動,電力品質監視,精密産業用計測,オーディオおよび音声帯域,通信などがあります。

デュアルスロープADC

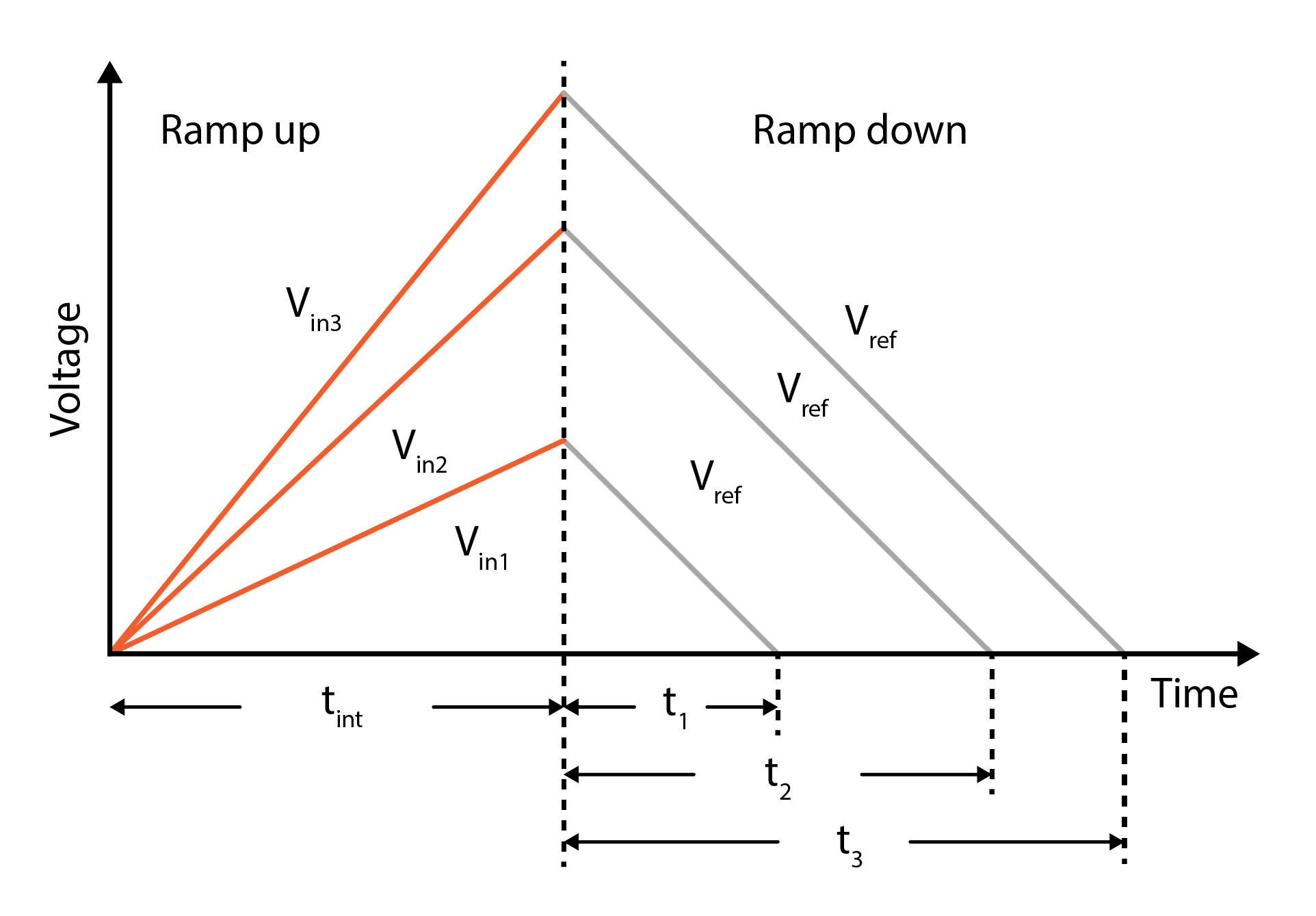

デュアルスロープADCは正確ですが、それほど高速ではありません。このADCがアナログ値をデジタル値に変換する主な方法は、積分器を使用することです。電圧が入力され、一定期間「上昇」します。次に、逆極性の既知の電圧が印加されゼロまで戻します。ゼロに達するとシステムは、ランアップ時間とランダウン時間を比較し、そのリファレンス信号が何であったかを知ることにより、入力電圧を計算します。ランアップ時間とランダウン時間は、この手法が命名された2つの勾配です。

この反復プロセスは信頼できますが、時間がかかり、SARやデルタシグマADCとは異なり、両方を実現することはできないため、分解能と速度の間には常にトレードオフがあります。その結果、デュアルスロープ、つまり「積分型ADC」は、ハンドヘルドマルチメータなどのアプリケーションで使用され、DAQアプリケーションでは使用されていません。

コンパレータ,タイマー,コントローラを表示する一般的な統合アンプ

コンパレータ,タイマー,コントローラを表示する一般的な統合アンプ

長所

- 非常に正確な計測

短所

- ランプアップとランプダウンの反復により変換時間が遅い

用途

デュアルスロープADCのアプリケーションとして、ハンドヘルドおよびベンチトップマルチメータなどがあります。

フラッシュADC

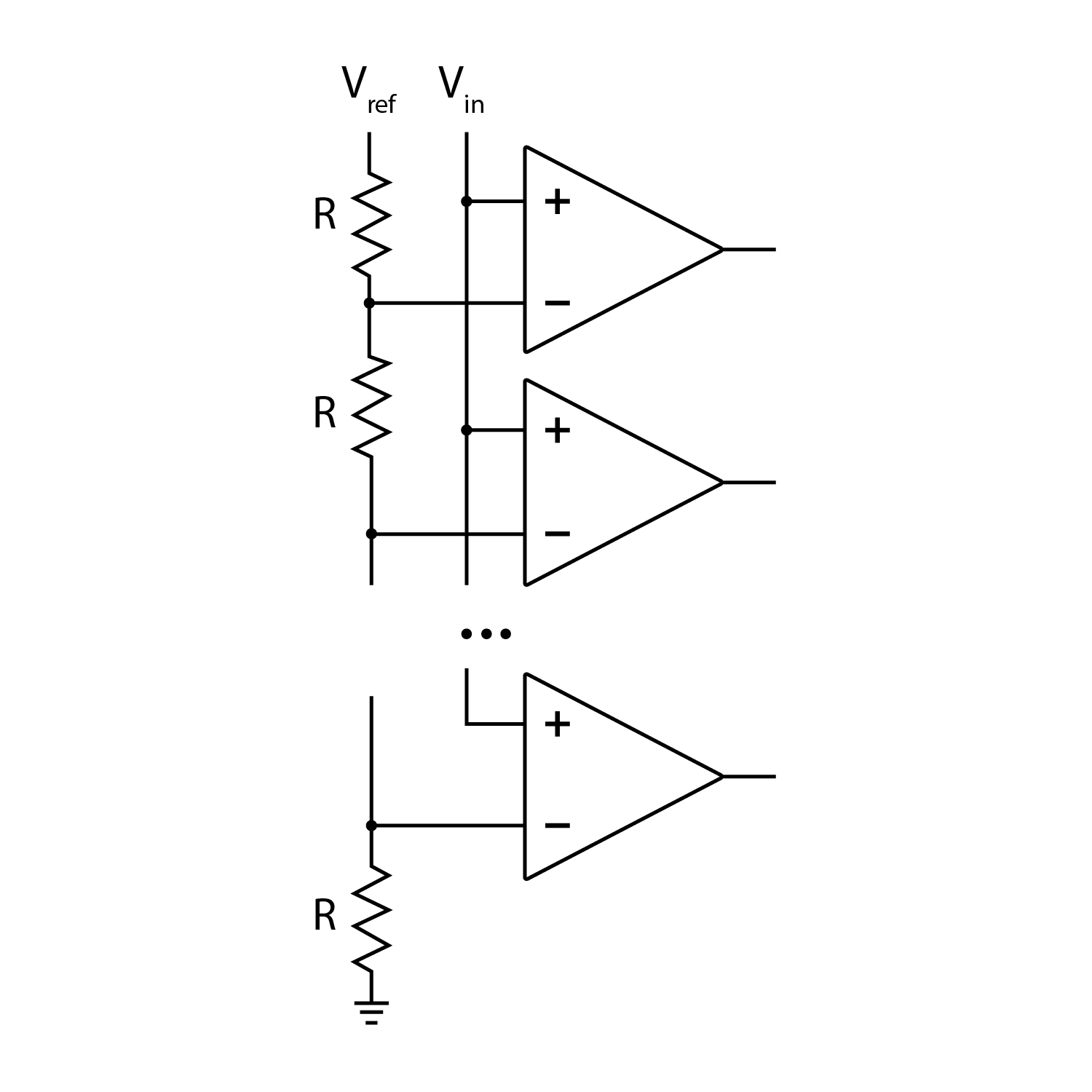

フラッシュADCは高速で実質的に遅延なく動作します。そのため、可能な限り高いサンプルレートが必要な場合に選択できる構造です。既知の基準値と比較することでアナログをデジタル信号に変換します。変換プロセスで使用される既知の基準値が多いほど、より高い精度を実現できます。たとえば、10ビットの分解能を持つフラッシュADCが必要な場合、入力されるアナログ信号を1024の既知の値と比較する必要があります。8ビットの分解能では256の既知の値が必要になります。

必要な分解能が高くなるほど、フラッシュADCはより大きく、より多くの電力を必要とします。そしてサンプルレートを下げる必要があります。

そのため、8ビットの分解能は一般的にこれらのADCの「スイート スポット」です。フラッシュADCは低いGS/sで動作しても、8ビットの分解能を維持できます。

フラッシュADC図

フラッシュADC図

長所

- 最速のADCタイプ

- 遅延の無い瞬時変換

短所

- 回路はビット数ごとに大きくなり、より多くの電力を消費

- 分解能は事実上8ビットに制限

用途

フラッシュADCのアプリケーションには、最高速のデジタルオシロスコープ,マイクロ波計測,光ファイバー,レーダー検出,広帯域無線などがあります。

パイプラインADC

SARおよびデルタシグマADCよりも高いサンプルレートを必要としますが、フラッシュADCのように超高速を必要としないアプリケーションにはパイプラインADCがあります。

前のセクションで説明したように、フラッシュADCのコンパレータはすべて同時にラッチされるため遅延がありません。ただし、これには多くの消費電力が必要です。特に、より高いビット分解能を実現するためにコンパレータを使用する場合はますます多くなります。ただし、パイプラインADCでは、アナログ信号がすべてのコンパレータによって同時にラッチされるわけではないため、アナログをデジタル値に変換するために必要なエネルギーが分散されます。したがって、フラッシュコンパレータは2〜3サイクルの準シリアルプロセスに「パイプライン化」されます。これには、大きなエネルギーなしでより高い分解能を実現できるという利点がありますが、2つの弱点を持ちます。サンプルレートは、純粋なフラッシュADCほど高くすることはできません。遅延が通常3サイクル発生しある程度軽減できますが、完全になくすことはできません。

パイプラインADCの図

パイプラインADCの図

これらのADCは、2~3 MS / s~100 MS / s(1 GS / sも可能)のアプリケーション向けの一般的なアーキテクチャです。これを超えるサンプルレートでは、通常、フラッシュADCテクノロジが採用されています。パイプラインADCの分解能は、より低いサンプルレートでは16ビット程度ですが、通常、最高のサンプルレートでは8ビットです。繰り返しますが、速度と分解能の間には常にトレードオフがあります。

長所

- ピュアフラッシュADCタイプとほぼ同じ速度(SARおよびデルタシグマより高速)

短所

- シリアルの「パイプライン」変換プロセスによる遅延

- ビット分解能によって制限される最大サンプルレート

用途

パイプラインADCのアプリケーションには、デジタルオシロスコープ,レーダー,ソフトウェアラジオ,スペクトラムアナライザ,HDビデオ,超音波イメージング,デジタルレシーバ,ケーブルモデム,イーサネットなどがあります。

まとめ

各ADC技術にはそれぞれの用途があります。計測アプリケーションはユーザによってさまざまなためADCを一つに決めることはできません。

| 基準 | SAR ADC | シグマデルタ(ΔΣ)ADC |

|---|---|---|

| 最高の振幅軸分解能が必要な場合(熱電対などの低速信号に対しても!) | 通常は最大16または18ビット | より良い選択。24ビットは、現在のΔΣカードの事実上の標準 |

| 安価なマルチプレクスADカードを使用する必要がある場合 | 選択のみ。短時間のスキューエラーが問題にならない場合、複数のチャネルの単一のSAR ADCをMUXして安価なDAQシステムを作成可能 | |

| 可能な限り高いサンプルレートが必要な場合 | より良い選択。最大10 MS /秒のサンプリングでデータを取得するためのSAR ADCがある | オンボードDSP処理により、ΔΣADCはSAR ADCに比べてサンプルレートが高くなる |

| AAF(アンチエイリアシングフィルタリング)が必要な場合 | SAR ADCに追加するには高価で複雑 | AAFはΔΣADCに固有であるため、より良い選択 |

| 最高のS / N比が必要な場合 | 唯一の選択。DEWESoft独自のDualCoreADC®テクノロジで最大160dBを達成可能 | |

| 不自然な信号がほとんど記録される場合(矩形波など) | 矩形波の表現に優れてる |

DEWESoftは、ほとんどの機種にアンチエイリアスフィルタが組み込まれた24ビットシグマデルタADCを使用していますが、SIRIUS DAQシステム製品ラインで1 MS / sの最大サンプルレートを達成するために、16ビットSAR ADCも使用します。これらのSARベースのDEWESoftシステムは、5次100 kHzフィルタの強力なAAFフィルタを実装しています。

採用するADCテクノロジの選択は、常にアプリケーションの要求仕様を考える必要があります。主に静的および準静的(低速)信号を計測する場合は、明らかに超高速システムは必要ありませんが、できるだけ多くの振幅軸分解能を持つシステムが必要です。

業界で使用されている固定システム(ラックマウントシステム)には、通常要件はあまり変化しないため、システムを選択する方が簡単です。

ただしDAQシステムの場合、さまざまなアプリケーションで使用されているため、少し難しくなります。重要なのは、全体的なパフォーマンスが最高で、ノイズ,エイリアシング,陳腐化を防ぐ製品を選択することです。

関連ページ